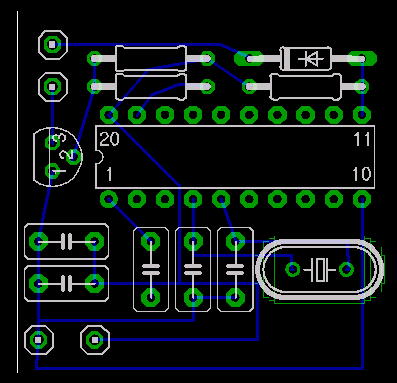

хм, и за ЭТО с людей дерут по $200… себестоимость все этого 282руб в ценах chip-and-dip 🙂

;------------------------------------------------------------------------------

; Hondainfo's Speed Limit Defencer

; AT89C4051 mikrokontroller assembly program

; V1.2 2003.10.22

;------------------------------------------------------------------------------

$mod51

;------------------------------------------------------------------------------

; Theory:

;

; The VSS signal (measured data)

; At 60 km/h Freq: 42 Hz

; At 100 km/h Freq: 70 Hz

; At 120 km/h Freq: 84 Hz

; At 170 km/h Freq: 119 Hz

; duty in all case:50%

;

; This program is a simple signal copy when the frequency of signal is below 119 Hz

; Above 119Hz, the program switches to Virtual mode and sends Virtual

; 119 Hz signals to ECU independ on Input signal frequency.

;

;------------------------------------------------------------------------------

;------------------------------------------------------------------------------

; Memory variables:

;------------------------------------------------------------------------------

; pin definition

VSS_IN EQU P3.7 ; Recieve VSS signal here

VSS_OUT EQU P1.7 ; artifical VSS signal to ECU (0: transistor is closed, 1: transistor is opened, pull the signal to Gr

VIRTUAL bit 001h ; mode: =1 Virtual, =0 real signal output

VSS_OLD bit 002h ; altering of sampled signal

COUNTR data 030h ; Real Counter counts the time beetween two VSS signal

COUNTV data 031h ; Virtual counter for artifical VSS signal output

;------------------------------------------------------------------------------

; Cнmdeffinition, interrupt table

;------------------------------------------------------------------------------

RESET code 00000h

org 0000h ;starting here after Reset

ljmp kezdet

org 0003h

reti

org 000bh ;Timer 0 interrupt

ljmp T0_int

org 0013h

reti

org 001bh

reti

org 0023h

reti

org 002bh

reti

org 30h

;------------------------------------------------------------------------------

; 22.1184 Mhz quartz

; Timer 0 interrupt aprox: 0,0434 ms time base for measuring milisecs

; - run 23040 times per a second

; time period: 43 us

; runing time max: 30 us

;------------------------------------------------------------------------------

T0_int: PUSH PSW

mov TL0,#0B0h ; software reload

mov TH0,#0FFh

mov TCON,#050h

;*****MEASURING VSS SIGNAL

jb VSS_IN,Ti0 ; jump if no signal (1->0 edge)

jnb VSS_OLD,Ti0 ; jump if previous sample similar

mov a,#192d ; there is signal, check the counter

clr c ; 192x0,0434ms=8,33msec (119 Hz)

subb A,COUNTR

cpl c ; If < = 8,33 msec then switch to virtual signal mode

mov VIRTUAL,c ; If > 8.33 msec then switch to Real signal mode

mov COUNTR,#0ffh ; Initial Real Counter

Ti0: mov c,VSS_IN ; sample altering

mov VSS_OLD,c

mov a,COUNTR

xrl a,#250d ; increment Real Counter, but max: 250

jz Ti1

inc COUNTR

;*****VIRTUAL COUNTER

Ti1: mov a,COUNTV

xrl a,#192d ; increment Virtual Counter 0-192 cycle

jnz Ti11

mov COUNTV,#0ffh

Ti11: inc COUNTV

;*****REAL MODE SIGNAL COPY

Ti2: jb VIRTUAL,Ti3 ; jump if Virtual mode

mov c,VSS_IN ; In Real Mode simple SIGNAL COPY

cpl c

mov VSS_OUT,c

sjmp Ti4

;*****VIRTUAL MODE ARTIFICAL SIGNAL OUTPUT

Ti3: mov a,#096d ; Virtual signaling above 170 kph

clr c ; send 0 to output (pull to the ground)

subb A,COUNTV ; when Virtual Counter < =96

cpl c ; send 1 to output (release)

mov VSS_OUT,c ; when Virtual Counter >96

Ti4: POP PSW

reti ; END OF INTERRUPT

;------------------------------------------------------------------------------

;Starting after Reset, int init

;------------------------------------------------------------------------------

kezdet: clr VSS_OUT ; init output

mov c,VSS_IN ; first altering

mov VSS_OLD,c

mov COUNTR,#250d

mov COUNTV,#000d

clr VIRTUAL

mov TMOD,#021h ; init timers T1 mode 2 (Auto Reload, Serial Port)

mov TL1,#0FFH ; T0 mode 1 (16 bit timer, software reload, Interrupt)

mov TH1,#0FFH ; serial port timing 9600 baud (use for testing)

mov TL0,#0B0h ; 65536d-80d-t to the counter init

mov TH0,#0FFh ;

mov SCON,#052H ; serial port mode 1

mov TCON,#050h ; Timer1 , Timer0 indul

mov IE,#092h ; RI/TI int enabled, T0 int enabled

ciklus: sjmp ciklus

end